英特尔展示面向更大尺寸封装的技术

作者: CBISMB

责任编辑: 张金祥

来源: ISMB

时间: 2025-06-03 12:51

关键字: 英特尔,更大尺寸,封装技术

浏览: 24

点赞: 0

收藏: 0

英特尔计划从2026年起生产封装尺寸达到12x12厘米的处理器和加速器,并计划从2028年起实现更大规模。技术上的改进将使这一切成为可能。

数十年来,更多的晶体管一直是高性能硬件的保证。但近年来,半导体行业开始采用一种新思路:制造更大的封装,并在其上安装越来越多的独立硅芯片(die)。英伟达在2025年3月就已揭示了这一趋势。预计到2027年,其将推出一款名为Rubin Ultra的GPU,该GPU将集成四个计算芯片和16个HBM(高带宽内存)堆栈。

这对封装技术而言是一项重大挑战。英特尔代工服务(Intel Foundry Services)希望通过改进其嵌入式多芯片互连桥接(EMIB)技术和封装工艺来应对。这些创新细节已于5月27日至30日在德克萨斯州达拉斯举行的电子元件技术会议(ECTC)上进行了详细介绍,《Tom's Hardware》对此进行了报道。

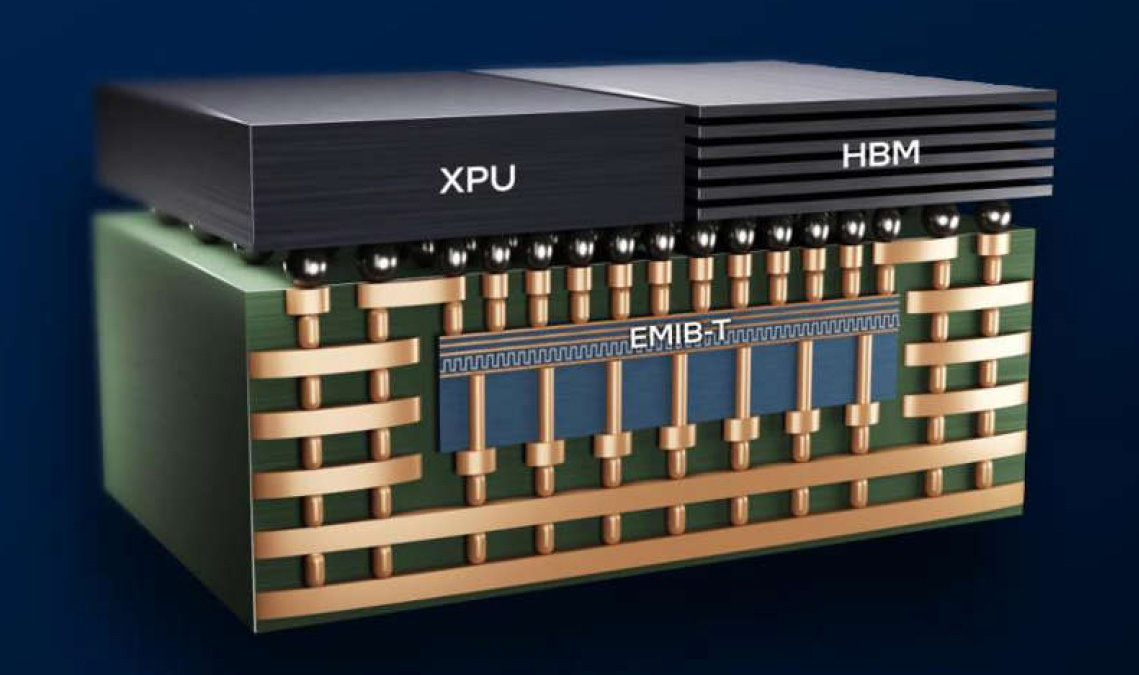

在会议上,英特尔工程师讨论了新版EMIB技术。该版本已在4月底的英特尔代工活动中首次亮相,其特点是首次集成了硅通孔(TSV)和电容器。这两项改进能够为用于两个小芯片(Chiplet)之间数据交换的收发器提供更可靠的电源。EMIB本身也是一个硅芯片,它能实现特别密集的触点连接——英特尔已将其触点密度从每平方毫米330个提升至772个。

为32 GBit/s/触点乃至更高速度做好准备

目前,单个触点的间距(Pitch)为36微米,据《Tom's Hardware》报道,未来有望降至约25微米。得益于更高的触点密度和优化的供电,新一代EMIB-T技术将能够支持HBM4内存的连接,或通过UCIe(通用小芯片互连快线)实现小芯片间的连接。

对于后者(UCIe),数据速率尤其具有挑战性:UCIe 2.0标准规定每个触点的数据速率为32 GBit/s,而Synopsys甚至支持高达40 GBit/s/触点。以往的EMIB技术在此方面有时会遇到问题:电源触点必须布置在硅桥之外,导致了更长的导线路径。通过采用TSV,现在可以将电源直接连接到需要的地方。集成的电容器则进一步稳定了电源电压,从而降低了对负载下电压骤降(voltage droop)的容差要求。

更温和的键合工艺与新型散热器

为了实现计划中的封装尺寸——从2026年起达到12x12厘米,从2028年起达到12x18厘米——封装工艺本身也需要改进。英特尔工程师为此展示了两项改进:首先是经过改良的热压键合(Thermokompressions-Bonding)技术,该技术用于将单个小芯片安装到封装基板上。通过降低键合过程中的温度,可以减少材料的变形。由于硅和基板在受热时膨胀系数不同,变形一直是个问题。

基板尺寸越大,这种差异膨胀造成的影响就越显著,可能导致连接断裂和良品率(Yield)下降。玻璃基板预计也将在此领域发挥作用——英特尔明确提到EMIB-T的小芯片连接器与这类基板兼容。通过这些技术,每个封装的硅片总面积目标是首先提升至光刻掩模版极限尺寸(Reticle Limit,通常为858平方毫米)的八倍,在第二阶段则提升至十二倍。英特尔展示了相关示例,包括采用四个计算芯片和12个HBM堆栈的12x12厘米封装,以及采用八个计算芯片和24个HBM堆栈的12x18厘米封装。

此外,英特尔还展示了一种新型集成散热器(IHS)设计。英特尔不再将其视为传统的金属顶盖,而是计划将其分解为一个平板和多个加强模块。后者将用于精确调节IHS与硅芯片之间的间距,而这种新结构旨在改善整体的散热效果。