台积电详解 3nm 工艺 FINFLEX 技术

作者: CBISMB

责任编辑: 张金祥

来源: ISMB

时间: 2022-06-20 09:56

关键字: 台积电 3nm

浏览: 9

点赞: 0

收藏: 0

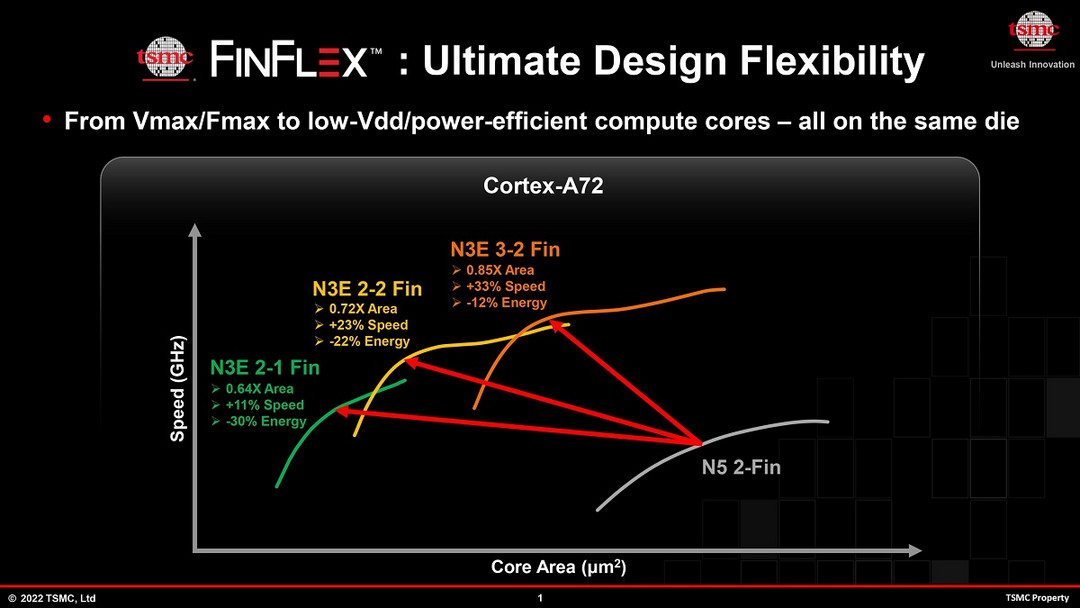

台积电(TSMC)在其2022年技术论坛上,介绍了N3制程节点使用的FINFLEX技术,扩展了工艺的性能、功率和密度范围,允许芯片设计人员使用相同的设计工具集为同一芯片上的每个关键功能块选择最佳选项。

N3制程节点使用的FINFLEX技术包括了以下特性和选项:

3-2 FIN - 最快的时钟频率和最高的性能满足最苛刻的计算需求

2-2 FIN - 高能效表现,在性能、功率和密度之间取得良好的平衡

2-1 FIN - 超高能效、最低功耗、最低泄漏和最高密度

台积电表示,近年来的一种趋势是采用混合架构的处理器,即高性能的内核与高能效的内核搭配使用,同时还辅以各种功能模块。借助FINFLEX技术,设计人员可以为同一个芯片上的这些功能模块选择最佳的工艺配置,优化每个模块同时不会影响其他模块。

无论从PPA(功率、性能、面积),以及上市和量产时间,加上一开始就考虑实现基于FINFLEX技术的定制配置,台积电认为其N3制程节点在工艺技术上将处于领先水平,可以为任何产品提供最广泛且灵活的设计范围。此外,台积电通过与EDA合作伙伴密切合作,让客户能够通过使用相同的工具集,在产品中充分利用FINFLEX技术。

根据此前的消息,台积电第二版3nm制程的N3B会在今年8月份率先投片,第三版3nm制程的N3E的量产时间可能由原来的2023年下半年提前到2023年第二季度。

据了解,N3E在N3基础上减少了EUV光罩层数,从25层减少到21层,逻辑密度低了8%,但仍然比N5制程节点要高出60%。